Re: вопросы по Verilog

Пт фев 01, 2013 17:50:31

придется думать что-то гениальное....

потому что прошивка на AHDL влезает и работает)

потому что прошивка на AHDL влезает и работает)

Re: вопросы по Verilog

Пт фев 01, 2013 19:10:00

Кажется вы не внимательны!

1) В исходном коде только один регистр ! IN_REG[15..0] , остальное всё логические действия !

2) Вы не разобрались как работать с портом ввода/вывода т.е. двунаправленным, и поэтому наверное код не работает..

Пример от Алтеры:

Тоесть читаем состояние порта когда ему присвоено состояние "Z"

В остальном, хорошо что двигаетесь вперёд..

1) В исходном коде только один регистр ! IN_REG[15..0] , остальное всё логические действия !

2) Вы не разобрались как работать с портом ввода/вывода т.е. двунаправленным, и поэтому наверное код не работает..

Пример от Алтеры:

- Код:

module bidirec (oe, clk, inp, outp, bidir);

// Port Declaration

input oe;

input clk;

input [7:0] inp;

output [7:0] outp;

inout [7:0] bidir;

reg [7:0] a;

reg [7:0] b;

assign bidir = oe ? a : 8'bZ ;

assign outp = b;

// Always Construct

always @ (posedge clk)

begin

b <= bidir;

a <= inp;

end

endmodule

Тоесть читаем состояние порта когда ему присвоено состояние "Z"

В остальном, хорошо что двигаетесь вперёд..

Re: вопросы по Verilog

Чт авг 22, 2013 22:59:01

Добрый день! Такая проблема. Есть код на Verilog, который, по идее, реализует машину состояний для инициализации динамической памяти. Проблема в том, что при компиляции в State Machine Viewer-е эта машина состояний просматривается как пустая. Соответственно, в железке ничего не срабатывает. Уменьшил код до такого:

Все равно, машина состояний остаётся пустой, регистр init_done_reg никогда не становится единицей, хотя ошибится тут трудно, вроде как. Уже бьюсь головой об стену. Что я делаю не так?

Спойлер

- Код:

module MemInit (

//Тактирование

input wire mem_clk_133MHz,

input wire mem_clk_lock,

input wire nreset,

output wire init_done,

//output wire [2:0] init_cmd,

//output wire [21:0] init_adr,

input wire cmd_ack

);

/*****************************************************************/

//Описание состояний

localparam [3:0]

state_begin = 4'b0000,

state_loadreg1 = 4'b0001,

state_iwait = 4'b0010,

state_prech = 4'b0011,

state_prwait = 4'b0100,

state_fautor = 4'b0101,

state_fwait = 4'b0110,

state_sautor = 4'b0111,

state_swait = 4'b1000,

state_loadmr = 4'b1001,

state_loadreg2 = 4'b1010,

state_done = 4'b1111;

/*****************************************************************/

//регистры

reg [3:0] state = state_begin;

reg [3:0] next_state = state_begin;

reg init_done_reg = 0, next_init_done_reg;

reg [31:0] cycle_counter = 0;

reg [31:0] next_cycle_counter = 0;

assign init_done = init_done_reg;

/*****************************************************************/

//Тактирование

wire clk;

assign clk = mem_clk_133MHz & mem_clk_lock;

always @(posedge clk or negedge nreset) begin

if(!nreset) begin //Сброс

state <= state_begin;

init_done_reg <= 0;

end

else begin //Нормальная работа

state <= next_state;

init_done_reg <= next_init_done_reg;

cycle_counter <= next_cycle_counter;

end

end

/*****************************************************************/

//Машинка состояний

always @* begin

next_state = state;

next_init_done_reg = init_done_reg;

next_cycle_counter = cycle_counter + 32'b1;

case (state)

state_begin:

begin

next_cycle_counter = 0;

next_state = state_iwait;

end

state_iwait:

begin

if(cycle_counter >= 32'd133000) next_state = state_done;

end

state_done:

begin

next_init_done_reg = 1;

end

default:

begin

next_state = state_begin;

next_init_done_reg = 0;

end

endcase

end

endmodule

Все равно, машина состояний остаётся пустой, регистр init_done_reg никогда не становится единицей, хотя ошибится тут трудно, вроде как. Уже бьюсь головой об стену. Что я делаю не так?

Re: вопросы по Verilog

Вт окт 22, 2013 18:42:43

Хочу освоить verilog

Создал программу счетчика

module q1 (led [29:0], clk);

input clk;

output reg [29:0]led;

always @(posedge clk)

begin

#100

led <= led + 1'd1;

end

endmodule

Почему задержка не срабатывает?

Создал программу счетчика

module q1 (led [29:0], clk);

input clk;

output reg [29:0]led;

always @(posedge clk)

begin

#100

led <= led + 1'd1;

end

endmodule

Почему задержка не срабатывает?

Re: вопросы по Verilog

Вт окт 22, 2013 20:37:51

Pawel91 писал(а):Почему задержка не срабатывает?

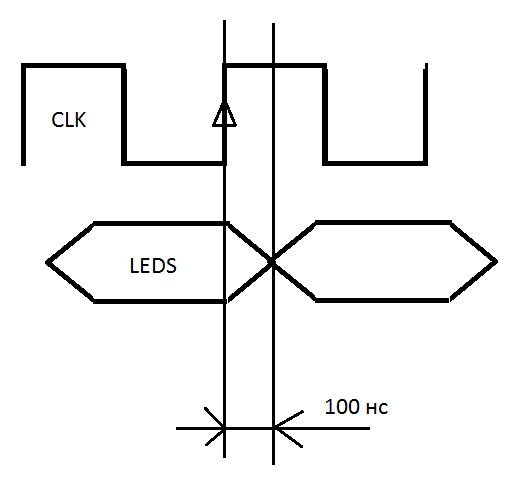

Что значит, не срабатывает? Написанное вами значит, что между положительным фронтом clk и изменением значения регистра leds будет задержка 100 нс. Но частота изменений регистра leds будет определяться частотой тактирования clk. Вот вам картинка для пояснения:

Re: вопросы по Verilog

Ср окт 23, 2013 11:25:13

Я так и предполагал, но симуляция в квартус выдает другое.

Задержка получается 6.819

(картинку загрузить не получилось((()

Задержка получается 6.819

(картинку загрузить не получилось((()

Re: вопросы по Verilog

Ср окт 23, 2013 19:20:08

Не уверен что верилог сильно отличается, но в вхдл, задержка имеет смысл только в моделировании (например что бы задать смещение сигналов), а в синтезе (речь как я понял именно о синтезе) команда задержки не работает.

Re: вопросы по Verilog

Ср окт 23, 2013 19:28:33

Я вот как раз и делал моделирование  , modelsim пока не осилил, делал во встроенной в 13 квартусе системе моделирования(waveform editor), указал на конкретно временное моделирование, я вообще делаю лабы студентам, мне нужно полностью изучить этот язык, так как лабы будут на освоение этого языка. Вот хочу научиться как правильно писать задержки для модулей.

, modelsim пока не осилил, делал во встроенной в 13 квартусе системе моделирования(waveform editor), указал на конкретно временное моделирование, я вообще делаю лабы студентам, мне нужно полностью изучить этот язык, так как лабы будут на освоение этого языка. Вот хочу научиться как правильно писать задержки для модулей.

Re: вопросы по Verilog

Ср окт 23, 2013 22:50:37

Pawel91 писал(а):Я вот как раз и делал моделирование

А какой период у источника тактового сигнала? Может, ваша задержка кратна этому периоду?

Re: вопросы по Verilog

Чт окт 24, 2013 06:02:40

Период разный делал и 200 и 500 нс. Задержка одна и таже

Re: вопросы по Verilog

Пт окт 25, 2013 08:31:33

Здравствуйте! Помогите разобраться в конечных автоматах на верилоге для альтеры.

Что можно почитать? С чего начать?

Что можно почитать? С чего начать?

Re: вопросы по Verilog

Пт окт 25, 2013 22:05:29

Поддерживаю вопрос порекомендуйте пожалуйста русскоязычную литературу, раскрывающую синтаксис и семантику языка Verilog HDL, а то до сих пор не могу разобраться с функциями следующих команд  :

:

cmos

deassign

pmos

pull0

pull1

pullup

pulldown

rcmos

release

rnmos

rpmos

rtran

rtranif0

rtranif1

specparam

strength

strong

notif0

notif1

strong1

tran

tranif0

tranif1

small

medium

large

force

cmos

deassign

pmos

pull0

pull1

pullup

pulldown

rcmos

release

rnmos

rpmos

rtran

rtranif0

rtranif1

specparam

strength

strong

notif0

notif1

strong1

tran

tranif0

tranif1

small

medium

large

force

Re: вопросы по Verilog

Пт ноя 01, 2013 14:20:30

Помогите с мелочью.

пишу строчку :

assign CLK1=CLK2;

у меня CLK1 бежит как надо, а CLK2 просто включается в единицу и все, как правильно будет написать?

пишу строчку :

assign CLK1=CLK2;

у меня CLK1 бежит как надо, а CLK2 просто включается в единицу и все, как правильно будет написать?

Re: вопросы по Verilog

Пт ноя 01, 2013 14:22:19

Попробуйте

wire CLK1 = CLK2

wire CLK1 = CLK2

Re: вопросы по Verilog

Пт ноя 01, 2013 14:53:13

так не работает,мне надо вход с выходом напрямую связать(

Re: вопросы по Verilog

Пт ноя 01, 2013 14:55:32

Т.е создать обратную связь?

Re: вопросы по Verilog

Пт ноя 01, 2013 15:12:42

Сделать перенаправление) Т.е есть альтерка, на одну ногу приходит одно, с другой ноги выходит тоже самое, в данном случае клок.

Re: вопросы по Verilog

Пт ноя 01, 2013 15:20:51

попробуйте

assign CLK2=CLK1

assign CLK2=CLK1

Re: вопросы по Verilog

Пт ноя 01, 2013 15:28:31

так тоже не прокатывает,делал уже)

Re: вопросы по Verilog

Пт ноя 01, 2013 15:37:03

А какая частота ?