Некорректная работа прерываний T1 с двух каналов (CTC)

Сб сен 04, 2021 22:56:44

Котаны, всем привет!

Просьба тапками не бросаться - только начал осваивать Attiny 2313. Изучаю по книге Белова

Сейчас ковыряюсь с таймерами.

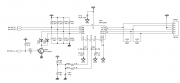

Ниже кусок извращенского кода, который ведет себя странно (или, скорее всего, я еще не догоняю).

Хочу понять механику работы прерываний для T1 при совпадении с двух каналов.

В текущем виде в обработчиках chnlA/chnlB при значениях TCCR1A 0x40 и 0x10 соответственно сигнала нет на ногах ОС1A/OC1B.

Опытным путем выявил, если и там, и там 0х50, то сигнал идет на 2 канала. И самое странное: если значения реверсные 0х10 и 0х40, то сигналы идут с разной частотой и небольшим сдвигом по фазе

Догадки есть, но почему тишина при "родных" значениях для каналов?

Просьба тапками не бросаться - только начал осваивать Attiny 2313. Изучаю по книге Белова

Сейчас ковыряюсь с таймерами.

Ниже кусок извращенского кода, который ведет себя странно (или, скорее всего, я еще не догоняю).

Хочу понять механику работы прерываний для T1 при совпадении с двух каналов.

В текущем виде в обработчиках chnlA/chnlB при значениях TCCR1A 0x40 и 0x10 соответственно сигнала нет на ногах ОС1A/OC1B.

Опытным путем выявил, если и там, и там 0х50, то сигнал идет на 2 канала. И самое странное: если значения реверсные 0х10 и 0х40, то сигналы идут с разной частотой и небольшим сдвигом по фазе

Догадки есть, но почему тишина при "родных" значениях для каналов?

Спойлер

- Код:

.cseg

.org 0x00

rjmp reset

.org 0x04

rjmp chnlA

.org 0x0C

rjmp chnlB

; ---------- Модуль инициализации ----------

reset:

ldi temp, RAMEND

out SPL, temp

ldi temp, 0x18 ; Инициализация порта РВ на вывод: PB3=1 (15) и PB4=1 (16)

out DDRB, temp

clr temp

out DDRD, temp ; Порт PD на ввод DDRD=0

out PORTB, temp ; Низкий уровень => отключаем динамик

ldi temp, 0x7F

out PORTD, temp ; Включение внутренних резисторов

ldi temp, 0x80 ; Выключение компаратора

out ACSR, temp

; ---------- Инициализация таймера/счетчика T1 ----------

clr temp

out TCCR1A, temp ; Отключаем каналы А, В

ldi YH, 0x0A

ldi YL, 0x8C

out OCR1BH, YH

out OCR1BL, YL

ldi XH, 0x12

ldi XL, 0x8C

out OCR1AH, XH

out OCR1AL, XL

ldi temp, 0x09

out TCCR1B, temp ; Режим СТС и предделитель 1

ldi temp, 0x60

out TIMSK, temp ; Маска прерываний: разрешены по совпадению канала А и В

out TIFR, temp ; Очищаем флаг совпадения по каналу А и В

sei ; Разрешение прерываний

; ---------- Конец модуля инициалиации ----------

loop: nop

rjmp loop

chnlB:

ldi ocrB, 0x10

out TCCR1A, ocrB ; 0x10 (канал В)

reti

chnlA:

ldi ocrA, 0x40

out TCCR1A, ocrA ; 0x40 (канал A)

reti

Re: Некорректная работа прерываний T1 с двух каналов (CTC)

Вс сен 05, 2021 00:29:08

В текущем виде в обработчиках chnlA/chnlB при значениях TCCR1A 0x40 и 0x10 соответственно сигнала нет на ногах ОС1A/OC1B.

Сигнала нет, т.к. у вас выбран режим "Normal port operation, OC1A/OC1B disconnected."

In Clear Timer on Compare or CTC mode (WGM13:0 = 4 or 12), the OCR1A or ICR1 Register

are used to manipulate the counter resolution. In CTC mode the counter is cleared to zero when

the counter value (TCNT1) matches either the OCR1A (WGM13:0 = 4) or the ICR1 (WGM13:0 =

12).

Читайте даташит.

Ну, и написан у вас не код, а какая-то дребедень.

Скачайте avr-gcc, и забудьте про asm, как страшный сон.

Re: Некорректная работа прерываний T1 с двух каналов (CTC)

Вс сен 05, 2021 02:55:01

Хочу понять механику работы прерываний для T1 при совпадении с двух каналов.

СТС режим – это очистка (сброс в ноль) счётного регистра TCNT1 при совпадении со значением регистра OCR1A. А при совпадении регистра TCNT1 с регистром OCR1B счётный регистр TCNT1 не сбрасывается, а продолжает считать. Таким образом, если регистр OCR1B будет по значению больше регистра OCR1A, то прерывание по каналу В не произойдёт, так как при совпадении регистра TCNT1 и регистра OCR1A счётный регистр TCNT1 очистится и значит до значения регистра OCR1B не сможет досчитать. А если значение регистра OCR1B будет меньше значения регистра OCR1A, то оба прерывания по каналу В и по каналу А будут работать как положено.

Re: Некорректная работа прерываний T1 с двух каналов (CTC)

Вс сен 05, 2021 05:20:03

Ассемблер нужно изучить, для того, чтобы понимать позже на уровне дизасма, что происходит.

Re: Некорректная работа прерываний T1 с двух каналов (CTC)

Вс сен 05, 2021 08:22:29

И чего все так от ассемблера шарахаются?

Вполне себе нормальный инструмент для большинства прикладных приложений.

Чаще вопрос не в языке, а в необходимом уровне изучения аппаратных модулей микроконтроллера.

Да в тонкостях взаимосвязи настроек этих модулей и ядра МК.

Вполне себе нормальный инструмент для большинства прикладных приложений.

Чаще вопрос не в языке, а в необходимом уровне изучения аппаратных модулей микроконтроллера.

Да в тонкостях взаимосвязи настроек этих модулей и ядра МК.

Re: Некорректная работа прерываний T1 с двух каналов (CTC)

Вс сен 05, 2021 11:46:28

Читайте даташит.

Ну, и написан у вас не код, а какая-то дребедень.

Скачайте avr-gcc, и забудьте про asm, как страшный сон.

Ну, и написан у вас не код, а какая-то дребедень.

Скачайте avr-gcc, и забудьте про asm, как страшный сон.

По поводу говнокода критика принимается. Назначение чисто экспериментальное.

По остальному не соглашусь: в битах COM1A0 и COM1B0 регистра TCCR1A как раз стоят "1", что говорит о том, что сигналы OC1A/OC1B уже активированы.

TCCR1B выставлен правильно (режим СТС, без предделителя).

Т.е. значения 0х40 и 0х10 в прерываниях корректные для канала А и В: COM1A0 = 1 и COM1B0 = 1 соответственно. Почему при этом тишина - непонятно. Еще непонятнее, почему сигнал идет, но при двух активных каналах 0х50 (COM1A0 = 1 и COM1B0 = 1 одновременно). Ну и совсем взрыв мозга, почему при противоположных значениях COM1A0/COM1B0 для каждого канала есть писк, но какой-то странный: со смещением по фазе и частоте.

Пардон, если сумбурно.

Re: Некорректная работа прерываний T1 с двух каналов (CTC)

Вс сен 05, 2021 16:11:12

Какая у тебя Attiny? 2313 или 2313А? Они чуть разные. И читать надо ОРИГИНАЛЬНЫЙ ДАТАШИТ.

Re: Некорректная работа прерываний T1 с двух каналов (CTC)

Вс сен 05, 2021 16:24:00

Какая у тебя Attiny? 2313 или 2313А? Они чуть разные. И читать надо ОРИГИНАЛЬНЫЙ ДАТАШИТ.

2313A. Там вроде по энергосбережению разница по сравнению с 2313?

Re: Некорректная работа прерываний T1 с двух каналов (CTC)

Вс сен 05, 2021 17:23:08

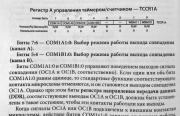

Открываем оригинальный даташит

https://www.microchip.com/en-us/product ... ment-table

ищем таблицу 12-5. Из неё узнаём, что режим СТС есть двух типов: со сбросом по значению регистра ICR1 или OCR1A.

Далее открываем таблицу 12-2 и выставляем биты регистра TCCR1A в соответствии с ней. Затем выставляем предделитель таймера и он начинает тикать.

Также обязательно помним, что флаг компаратора взводится не в текущем такте (такт таймера, а не системный!) совпадения значений, а лишь в следующем.

Добавлено after 6 minutes 30 seconds:

Энергопотреблением отличаются 2313 и 2313V. 2313A другой кристалл.

https://www.microchip.com/en-us/product ... ment-table

ищем таблицу 12-5. Из неё узнаём, что режим СТС есть двух типов: со сбросом по значению регистра ICR1 или OCR1A.

Далее открываем таблицу 12-2 и выставляем биты регистра TCCR1A в соответствии с ней. Затем выставляем предделитель таймера и он начинает тикать.

Также обязательно помним, что флаг компаратора взводится не в текущем такте (такт таймера, а не системный!) совпадения значений, а лишь в следующем.

Добавлено after 6 minutes 30 seconds:

2313A. Там вроде по энергосбережению разница по сравнению с 2313?

Энергопотреблением отличаются 2313 и 2313V. 2313A другой кристалл.

Re: Некорректная работа прерываний T1 с двух каналов (CTC)

Пн сен 06, 2021 06:43:06

kas1830 Как вариант к вышесказанному.

Периферия предназначена для разгрузки ядра. В Вашем случае можно обойтись без прерываний

Спойлер

- Код:

.include "tn2313Adef.inc"

.def temp=r16

;.def ocrA=r17

;.def ocrB=r18

.cseg

; .org 0x00

; rjmp reset

; .org 0x04

; rjmp chnlA

; .org 0x0C

; rjmp chnlB

; ---------- Модуль инициализации ----------

reset:

ldi temp, RAMEND

out SPL, temp

ldi temp, 0x18 ; Инициализация порта РВ на вывод: PB3=1 (15) и PB4=1 (16)

out DDRB, temp

clr temp

out DDRD, temp ; Порт PD на ввод DDRD=0

out PORTB, temp ; Низкий уровень => отключаем динамик

ldi temp, 0x7F

out PORTD, temp ; Включение внутренних резисторов

SBI ACSR,ACD ; Выключение компаратора

; ldi temp, 0x80 ; Выключение компаратора

; out ACSR, temp

; ---------- Инициализация таймера/счетчика T1 ----------

ldi YH, 0x0A

ldi YL, 0x8C

out OCR1BH, YH

out OCR1BL, YL

out OCR1AH, YH

out OCR1AL, YL

LDI R16,1<<WGM13|1<<WGM12;|1<<CS10 ; Режим сравнения ICR1 и предделитель 1

OUT TCCR1B,R16

LDI R16,1<<COM1A1|1<<COM1B1|1<<COM1A0|0<<COM1B0|1<<WGM11;|1<<WGM10

OUT TCCR1A,R16 ;противофазные импульсы A и B

; LDI R16,1<<COM1A1|1<<COM1B1|1<<COM1A0|1<<COM1B0|1<<WGM11;|1<<WGM10

; OUT TCCR1A,R16 ;синфазные импульсы A и B

ldi XH, 0x12

ldi XL, 0x8C

out ICR1H, XH

out ICR1L, XL

LDI R16,1<<WGM13|1<<WGM12|1<<CS10 ; Режим сравнения ICR1 и предделитель 1

OUT TCCR1B,R16

; ldi temp, 0x60

; out TIMSK, temp ; Маска прерываний: разрешены по совпадению канала А и В

; out TIFR, temp ; Очищаем флаг совпадения по каналу А и В

; sei ; Разрешение прерываний

; ---------- Конец модуля инициалиации ----------

loop:

rjmp loop

.EXIT

Периферия предназначена для разгрузки ядра. В Вашем случае можно обойтись без прерываний

Re: Некорректная работа прерываний T1 с двух каналов (CTC)

Пн сен 06, 2021 09:44:21

ТС, скачай MicrochipStudio и запусти свою программу в симуляторе. Там всё наглядно.

Re: Некорректная работа прерываний T1 с двух каналов (CTC)

Пн сен 06, 2021 11:17:36

Для 2313/2313а и Т1 достаточно симулятора даже в АВРстудио 4.19

Re: Некорректная работа прерываний T1 с двух каналов (CTC)

Пн сен 06, 2021 23:56:44

У меня Microchip Studio 7.0

В режиме отладки по F11 все четко прыгает по прерываниям. Соответствующие флаги выставляются/снимаются. Вроде, и в железе все должно работать, ан нет!

А как симуляцию запустить? Научите пжл. Сейчас выбрано Simulator в debugger/programmer. Не работал ни разу с ним.

В режиме отладки по F11 все четко прыгает по прерываниям. Соответствующие флаги выставляются/снимаются. Вроде, и в железе все должно работать, ан нет!

А как симуляцию запустить? Научите пжл. Сейчас выбрано Simulator в debugger/programmer. Не работал ни разу с ним.

Re: Некорректная работа прерываний T1 с двух каналов (CTC)

Вт сен 07, 2021 00:31:03

так отладка - это и есть работа в железе. Симуляция тогда нафик не нужна.

а в железе что должно происходить?

а в железе что должно происходить?

Re: Некорректная работа прерываний T1 с двух каналов (CTC)

Вт сен 07, 2021 05:49:37

Команды LDI в прерывании разрешая один канал запрещают другой. Поэтому на выходах OC1A, OC1B всегда 0. Если сделать как ниже получите импульсы сдвинутые по фазе примерно на четверть периода

Последним шагом будет отключение прерываний. На выходах OC1A, OC1B будут точно такие же импульсы.

- Код:

; ---------- Инициализация таймера/счетчика T1 ----------

LDI temp,1<<COM1A0|1<<COM1B0

; clr temp

out TCCR1A, temp ; Включить каналы А и В

;.

;.

;.

;.

chnlB:

; ldi ocrB, 0x10

; out TCCR1A, ocrB ; 0x10 (канал В)

reti

chnlA:

; ldi ocrA, 0x40

; out TCCR1A, ocrA ; 0x40 (канал A)

reti

Последним шагом будет отключение прерываний. На выходах OC1A, OC1B будут точно такие же импульсы.

Re: Некорректная работа прерываний T1 с двух каналов (CTC)

Вт сен 07, 2021 11:42:48

Если сделать как ниже получите импульсы сдвинутые по фазе примерно на четверть периода

Именно так! Если установить в регистре TCCR1A биты COM1A0 и COM1B0 в "1" прямо в модуле инициализации, то смысл прерываний отпадает. Все и так будет переключаться без проблем. Это я уже проделывал.

Все же непонятно, почему в соответствующих прерываниях для каналов А/В установка "родных" бит COM1A0/COM1B0 не дает сигнала с ног OC1A/OC1B. Ведь даже если они влияют друг друга, как было замечено ранее, все равно какое-то шевеление должно быть. Наверное, есть какая-то недокументированная особенность для режима СТС.

Я понимаю, что проблема высосана из пальца и, наверное, не стоит выеденного яйца, но все же хочу понять и доразобраться. Сейчас как зацикленный

Спасибо за понимание

Re: Некорректная работа прерываний T1 с двух каналов (CTC)

Вт сен 07, 2021 12:54:44

В режиме CTC регистры порта вывода необходимо взводить самому. Биты FOC тоже не работают. Поэтому отцепляем пины от компараторов, переключаем их и снова цепляем к компараторам. Компаратор таймера их только сбрасывает (в 0 или 1, если стоит инверсия). Если нужен полный автомат, то необходимо использовать что-то из режимов PWM.

Я в режимах NORMAL и CTC выводами управляю вручную.

Я в режимах NORMAL и CTC выводами управляю вручную.

Re: Некорректная работа прерываний T1 с двух каналов (CTC)

Вт сен 07, 2021 21:21:47

parovoZZ, спасибо за внимание к вопросу.

Вот это не совсем понял, можно пример?

Тут товарищ похожую проблему решал по каналу В

Согласен, так и будет. Просто хочу доразобраться наконец уже с этим.

Поэтому отцепляем пины от компараторов, переключаем их и снова цепляем к компараторам.

Вот это не совсем понял, можно пример?

Тут товарищ похожую проблему решал по каналу В

Если нужен полный автомат, то необходимо использовать что-то из режимов PWM.

Согласен, так и будет. Просто хочу доразобраться наконец уже с этим.

Re: Некорректная работа прерываний T1 с двух каналов (CTC)

Вт сен 07, 2021 22:56:54

PWM не всегда удобен - в этом режиме включаются буферы регистров сравнения, что не позволяет прямо в текущем цикле их менять.

Добавлено after 1 minute 42 seconds:

Вот это не совсем понял, можно пример?

COM обнуляешь и записываешь в регистр PORT нужное значение. Затем выставляешь биты COM.

Добавлено after 1 minute 42 seconds:

Поэтому отцепляем пины от компараторов, переключаем их и снова цепляем к компараторам.

Вот это не совсем понял, можно пример?

COM обнуляешь и записываешь в регистр PORT нужное значение. Затем выставляешь биты COM.

Re: Некорректная работа прерываний T1 с двух каналов (CTC)

Вт сен 07, 2021 23:32:15