Re: Микроконтроллеры STM32 - тонкости работы, отладочные пла

Чт май 12, 2022 17:07:02

Правильно. И ещё варистор, и лучше из новых, GMOV, например. Ну и автомат, обычный, класса С. А то вдруг действительно и 230 прилетит, а там может и 15 киловольт с подстанции притащится.

Возникает куча вопросов: зачем ставить такой ненадёжный LDO, откуда подрезаемые помехи и почему бы не защитить не только отладчик, но и собственно изделие?

И да, самое главное: не забудьте прилепить молниеотвод. С заземлением, разумеется.

Возникает куча вопросов: зачем ставить такой ненадёжный LDO, откуда подрезаемые помехи и почему бы не защитить не только отладчик, но и собственно изделие?

И да, самое главное: не забудьте прилепить молниеотвод. С заземлением, разумеется.

Re: Микроконтроллеры STM32 - тонкости работы, отладочные пла

Чт май 12, 2022 17:52:08

L1117-3.3 понижает с 9 до 3,3? Ой, многовато, особенно если он в SOT-223 корпусе. LDO - это low-drop, с низким падением напряжения. Для него оптимально 5-6 В понижать до 3,3. А вот с 9 - рискованно. Входное 15 В в даташите написано при выходном токе 0 мА. А при 800 мА указано входное 8,3 В, но при температуре кристалла 25°. На практике она начнет быстро повышаться и наступит хана. У меня был случай, когда пробило насквозь при перегреве. Так что тут надо пересмотреть концепцию питания. Можно поставить импульсный DC-DC понижатель, можно двуступенчато с 9 до 5 (только не LDO), а затем до 3,3 LDO

Re: Микроконтроллеры STM32 - тонкости работы, отладочные пла

Чт май 12, 2022 18:14:22

Не у меня ее тупо пробивает что на входе то на входе!(разочаровали они в общем). току у меня за 0,2 не перевалит. Поставлю еще крен 5в. Да не в этом проблема я же говорю с питанием я как-то разберусь это не проблема! микросхему выбивает когда подключаешь программатор к компу для отладки. Без сетевого напряжения все работает с питанием по отладчику и без отладки тоже все работает. Надо думать а то отлаживать ацп методом тыка долго....

Re: Микроконтроллеры STM32 - тонкости работы, отладочные пла

Вт июл 12, 2022 16:36:57

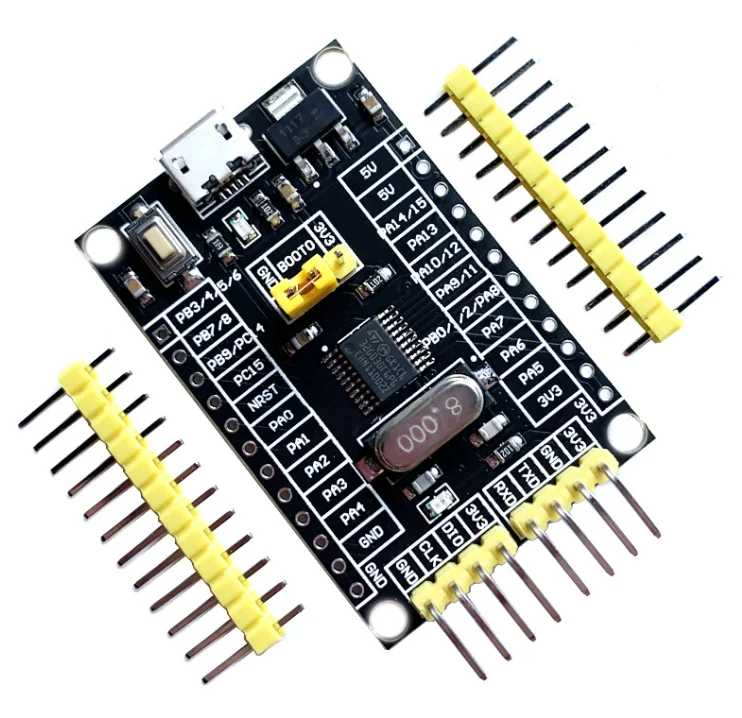

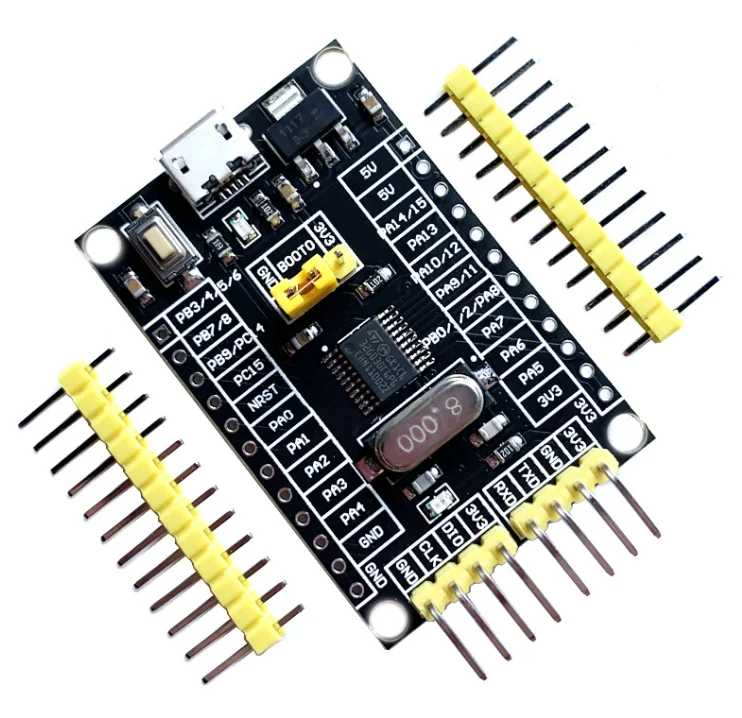

Здравствуйте. Надо "разлочить", видимо, клон STM32F103 Blue pill.

Юзаю оригинальный S-LINK v.2 через SWD. Нет связи, Core Reset не помогает. Вычитал , что якобы попробовать через UART1.

Я готов перерезать дорожки и т.п., но... объясните - смысл? Это только чтоб разлочить или тогда всегда прошивку надо будет заливать таким методом?

Потом. еще не понятно в одном ролике: дескать надо очистить память программ. Как это? Откуда программа, если модуль новый?

Юзаю оригинальный S-LINK v.2 через SWD. Нет связи, Core Reset не помогает. Вычитал , что якобы попробовать через UART1.

Я готов перерезать дорожки и т.п., но... объясните - смысл? Это только чтоб разлочить или тогда всегда прошивку надо будет заливать таким методом?

Потом. еще не понятно в одном ролике: дескать надо очистить память программ. Как это? Откуда программа, если модуль новый?

Re: Микроконтроллеры STM32 - тонкости работы, отладочные пла

Вт июл 12, 2022 16:39:27

dim3740, если connect under reset не помогает, то нужно подключить к USART1 (ЕМНИП, PA9/PA10) преобразователь UART-USB, выставить перемычки для загрузки во встроенный бутлоадер, включить питание и подключиться к USB компьютера. Стереть прошивку (можно заодно прошить новую).

Никакие дорожки для этого перерезать не нужно!

Единственная модификация, требуемая китайским "синим таблеткам" (если там, конечно, STM32 стоит, а не черт-те что) - удалить убогую 10к подтяжку DP+ USB, да припаять резистор 1к5 0603 между DP+ и соседней ногой PA15. Тогда можно будет спокойно программно пересоединяться, а не дергать каждый раз шнурок! Вот, ссылочка на мой ЖЖ

Никакие дорожки для этого перерезать не нужно!

Единственная модификация, требуемая китайским "синим таблеткам" (если там, конечно, STM32 стоит, а не черт-те что) - удалить убогую 10к подтяжку DP+ USB, да припаять резистор 1к5 0603 между DP+ и соседней ногой PA15. Тогда можно будет спокойно программно пересоединяться, а не дергать каждый раз шнурок! Вот, ссылочка на мой ЖЖ

Последний раз редактировалось Eddy_Em Вт июл 12, 2022 16:41:39, всего редактировалось 1 раз.

Re: Микроконтроллеры STM32 - тонкости работы, отладочные пла

Вт июл 12, 2022 16:41:16

спасибо. Что значит" стереть прошивку"? Ее там нет. И "заодно" не могу и (не хочу прошивать), потому что прошивку надо же отлаживать многократно. Поясните пожалуйста.

И про "дорожки".... модуль/плата впаяна в плату. Возможно (надо посмотреть) UART1 (его пины) уже используются. Как же не перерезать?

Я посмотрел Ваш ЖЖ. Это 2020 год. Мне кажется, что это ( что у меня) клоны, которые пошли в 2021 году из за дефицита полупроводников.

И про "дорожки".... модуль/плата впаяна в плату. Возможно (надо посмотреть) UART1 (его пины) уже используются. Как же не перерезать?

Я посмотрел Ваш ЖЖ. Это 2020 год. Мне кажется, что это ( что у меня) клоны, которые пошли в 2021 году из за дефицита полупроводников.

Re: Микроконтроллеры STM32 - тонкости работы, отладочные пла

Ср июл 13, 2022 23:45:46

Не обязательно шить через USART. Достаточно перевести МК в режим загрузчика. Тогда прошивка не будет мешать подключится по SWD.

На плате Blue pill для этого есть перемычки boot0 и boot1.

Читайте http://purebasic.mybb.ru/viewtopic.php?id=564#p7664

На плате Blue pill для этого есть перемычки boot0 и boot1.

Отладка в ОЗУ?dim3740 писал(а):И "заодно" не могу и (не хочу прошивать), потому что прошивку надо же отлаживать многократно.

Читайте http://purebasic.mybb.ru/viewtopic.php?id=564#p7664

Re: Микроконтроллеры STM32 - тонкости работы, отладочные пла

Чт июл 14, 2022 00:19:12

dim3740, я недавно получил липовую "синюю таблетку" (аж пять штук: повелся на дешевизну, по 117р за штучку!). Вместо STM32F103C6T6 там было распаяно нечто: мигало светодиодиком, выдавало себя за нормальный камень, делало вид, что прошивается. Но даже простейшая прошивка, которая должна была элементарно зажечь светодиод, не запустилась. Ну, можно будет по крайней мере использовать хоть печатные платки в качестве девборд для F072 или F303…

Жесть-то какая! Девборды - они на то и девборды, чтобы на них тренироваться. На худой конец - сговноляпить что-то временное, пока нормальную не сделал (абы это временное в таком виде десятилетиями потом не висело).

модуль/плата впаяна в плату

Жесть-то какая! Девборды - они на то и девборды, чтобы на них тренироваться. На худой конец - сговноляпить что-то временное, пока нормальную не сделал (абы это временное в таком виде десятилетиями потом не висело).

Re: Микроконтроллеры STM32 - тонкости работы, отладочные пла

Вт июл 19, 2022 12:51:05

del

Моя рукожопость зело велика: прошивку для C6T6 я делал с линкером от C8T6! Естественно, т.к. оперативы не 20кБ, а только 10, адрес стека вычислялся неправильно, что, похоже, приводило к хардфолту.

Моя рукожопость зело велика: прошивку для C6T6 я делал с линкером от C8T6! Естественно, т.к. оперативы не 20кБ, а только 10, адрес стека вычислялся неправильно, что, похоже, приводило к хардфолту.

Re: Микроконтроллеры STM32 - тонкости работы, отладочные пла

Сб дек 24, 2022 20:50:26

Надо кое куда поставить STm32G030 в корпусе TSSOP20. Внутреннему осцилятору я не особо доверяю, привык кварц цеплять везде. Так вот в корпусе тсоп20 OSC OUT назначить невозможно, но на алиэкспрессе есть отладочные платы где резонатор на 8МГц стоит. Можно его как-то повесить на один вывод, или китайцы сами не знают что сделали?

Re: Микроконтроллеры STM32 - тонкости работы, отладочные пла

Сб дек 24, 2022 21:23:19

А если выход с МСО взять? Антинаучно, но вдруг загенерит если пнуть?

Re: Микроконтроллеры STM32 - тонкости работы, отладочные пла

Сб дек 24, 2022 21:27:25

Можете подключить не кварц, а кварцевый генератор, у него как раз один выход. А на микроконтроллере включить режим HSE Bypass, он будет работать как вход внешнего генератора

Re: Микроконтроллеры STM32 - тонкости работы, отладочные пла

Сб дек 24, 2022 21:39:26

Таки это кварц.

Re: Микроконтроллеры STM32 - тонкости работы, отладочные пла

Сб дек 24, 2022 22:07:34

Таки это кварц.

Вот об этом я и говорю. Китайцы настолько тупые, или настолько умные?)

Я не удивлюсь если они его на OSC32 повесили)

Re: Микроконтроллеры STM32 - тонкости работы, отладочные пла

Сб дек 24, 2022 22:18:58

Я не удивлюсь если они его на OSC32 повесили)

Это запросто. Любопытство стоит дороже 216 руб. ? Re: Микроконтроллеры STM32 - тонкости работы, отладочные пла

Вс дек 25, 2022 16:45:59

Re: Микроконтроллеры STM32 - тонкости работы, отладочные пла

Вс дек 25, 2022 16:57:57

Эмм.. Когда лежать вот так вот россыпью, мелкие ножки с шагом 0,5 могут чутка загибаться и менять свой шаг. Было уже так. Поэтому я храню либо в ленте, в которой они приходят, либо на подложке рядами. Внавалку всё-такие не следует.

Re: Микроконтроллеры STM32 - тонкости работы, отладочные пла

Пн янв 16, 2023 18:35:15

Здравствуйте! Я подключаю дисплей на ST7735 к stm32f411ceu6, все работает 0.3 секунды после нажатия ресета, потом белый экран. При инициализации только - рябь 0.3сек, при заливке - заливка на 0.3 сек. Пробовал менять экран та же лажа только цвет заливки другой. Менял инициализацию на другие та же лажа, эту я уже успешно использовал до того. Подскажите пожалуйста люди добрые нубу местному, что я где ни так делаю.

Вот код если вдруг кто захочет глянуть

В теле программы только одна строка - вызов инициализации, пробовал в цикл сунуть безтолку.

Лоу левел инит вот так выглядит

Спасибо братцы!

Вот код если вдруг кто захочет глянуть

- Код:

void Send_CMD(uint8_t dat)

{ //Otpravka komand

GPIOB->ODR &= ~(1<<7); //ChipSelect loy

GPIOB->ODR &= ~(1<<6); //DC LoyLevel

SPI1->CR1 &= ~SPI_CR1_DFF;

while (!(SPI1->SR & SPI_SR_TXE));

SPI1->DR = dat;

while (!(SPI1->SR & SPI_SR_TXE));

while ((SPI1->SR & SPI_SR_BSY));

GPIOB->ODR |= (1<<7); //ChipSelect Up

}

void Send_DAT(uint8_t dat){ // danue 8 bit

GPIOB->ODR &= ~(1<<7); //ChipSelect loy

GPIOB->ODR |= (1<<6); //DC UpLevel

SPI1->CR1 &= ~SPI_CR1_DFF;

while (!(SPI1->SR & SPI_SR_TXE));

SPI1->DR = dat;

while (!(SPI1->SR & SPI_SR_TXE));

while ((SPI1->SR & SPI_SR_BSY));

GPIOB->ODR |= (1<<7); //ChipSelect Up

}

void Send_DAT16(uint16_t dat){ // danue 16 bit

GPIOB->ODR &= ~(1<<7); //ChipSelect loy

GPIOB->ODR |= (1<<6); //DC UpLevel

SPI1->CR1 |= SPI_CR1_DFF;

while (!(SPI1->SR & SPI_SR_TXE)){};

SPI1->DR = dat;

while (!(SPI1->SR & SPI_SR_TXE)){};

while ((SPI1->SR & SPI_SR_BSY)){};

GPIOB->ODR |= (1<<7); //ChipSelect Up

}

void LCD_Init(){

SPI1->CR1 |= SPI_CR1_SPE;//On Spi1

GPIOB->ODR |= (1<<4); //RST Hay

delay(15);

GPIOB->ODR &= ~(1<<4); //RST loy

delay(15);

GPIOB->ODR |= (1<<4); //RST Hay

delay(15);

Send_CMD(0x01);//Sbros nastroek

delay(50);

Send_CMD(0x28);//Programnoe wukl

Send_CMD(0xC0);//Obuchnaja pitanie

Send_CMD(0x11);//SlipOut

delay(150);

Send_CMD(0x29);//DispOn

Send_CMD(0x3A); //Format peredachi piksela

Send_DAT(0x55);

Send_CMD(0x20);//Vukl inversiu

Send_CMD(0x36);//hz

Send_DAT(0x80);

Send_DAT(0x40);

Send_DAT(0x08);

Send_DAT(0x20);

}

void SetWindow(uint16_t startX, uint16_t startY, uint16_t stopX, uint16_t stopY) {

Send_CMD(0x2A);

Send_DAT(startX >> 8);

Send_DAT(startX);

Send_DAT(stopX >> 8);

Send_DAT(stopX);

Send_CMD(0x2B);

Send_DAT(0x00);

Send_DAT(startY);

Send_DAT(stopY);

}

void bufer()

{

uint16_t x = 0, y = 0;

SetWindow(0, 0, 240, 320);

Send_CMD(0x2C);

while(y++ < 320)

{

x=0;

while(x++ < 240)

{

Send_DAT16(0xFFE0);//0xFFE0

}

}

}

В теле программы только одна строка - вызов инициализации, пробовал в цикл сунуть безтолку.

Лоу левел инит вот так выглядит

- Код:

#define RCC_PLLCFGR_PLLP_div2 (0x0U << RCC_PLLCFGR_PLLP_Pos)

#define RCC_PLLCFGR_PLLP_div4 (0x1U << RCC_PLLCFGR_PLLP_Pos)

#define RCC_CFGR_MCO2_HSE (0x2U << RCC_CFGR_MCO2_Pos)

#define RCC_CFGR_MCO2PRE_div1 (0x0U << RCC_CFGR_MCO2PRE_Pos)

#define RCC_CFGR_MCO1PRE_div1 (0x0U << RCC_CFGR_MCO1PRE_Pos)

#define RCC_CFGR_I2SSRC_PLLI2S (0x0U << RCC_CFGR_I2SSRC_Pos)

#define RCC_CFGR_MCO1_HSE (0x2U << RCC_CFGR_MCO1_Pos)

#include <stddef.h>

#include "stm32f411xe.h"

#ifdef __cplusplus

extern "C" {

#endif

int __low_level_init(void)

{

//Kvarc 25MHz, Proc 100MHzbegin

RCC->CR = _VAL2FLD(RCC_CR_HSITRIM,16) | RCC_CR_HSION | RCC_CR_HSEON;

while(!(RCC->CR & RCC_CR_HSERDY));

RCC->PLLCFGR = RCC_PLLCFGR_PLLSRC_HSE | _VAL2FLD(RCC_PLLCFGR_PLLQ,4) | _VAL2FLD(RCC_PLLCFGR_PLLN,192) | _VAL2FLD(RCC_PLLCFGR_PLLM,25) | RCC_PLLCFGR_PLLP_div2;

RCC->CR = _VAL2FLD(RCC_CR_HSITRIM,16) | RCC_CR_HSION | RCC_CR_HSEON | RCC_CR_PLLON;

while(!(RCC->CR & RCC_CR_PLLRDY));

RCC->CFGR = RCC_CFGR_MCO2_HSE | RCC_CFGR_MCO2PRE_div1 | RCC_CFGR_MCO1PRE_div1 | RCC_CFGR_I2SSRC_PLLI2S | RCC_CFGR_MCO1_HSE

| _VAL2FLD(RCC_CFGR_RTCPRE,8) | RCC_CFGR_PPRE2_DIV1 | RCC_CFGR_PPRE1_DIV2 | RCC_CFGR_HPRE_DIV1 | RCC_CFGR_SW_PLL;

FLASH->ACR = FLASH_ACR_PRFTEN | FLASH_ACR_ICEN | FLASH_ACR_DCEN | FLASH_ACR_LATENCY_3WS;

//*///Kvarc 25MHz, Proc 100MHz End

//Timer begin

RCC->APB1ENR |= RCC_APB1ENR_TIM2EN;// Taktirovanie Timer 2

__enable_irq ();

//Timer end

RCC->APB2ENR |= RCC_APB2ENR_SPI1EN; //Taktirovanie SPI1

RCC->AHB1ENR |= RCC_AHB1ENR_GPIOBEN;//Taktirovanie Port B

GPIOB->AFR[0] |= 0x00505000;

GPIOB->MODER |= ( GPIO_MODER_MODER4_0 | GPIO_MODER_MODER6_0 | GPIO_MODER_MODER7_0 | GPIO_MODER_MODER8_0 | GPIO_MODER_MODER10_0 ); // Port B Vihod

GPIOB->PUPDR |= ( GPIO_PUPDR_PUPD4_1 | GPIO_PUPDR_PUPD6_1 | GPIO_PUPDR_PUPD7_1 | GPIO_PUPDR_PUPD8_1 | GPIO_PUPDR_PUPD10_1 ); // Port B Vihod

GPIOB->MODER |= (GPIO_MODER_MODER3_1 | GPIO_MODER_MODER5_1);

GPIOB->OSPEEDR |= (3<<10)|(3<<6)|(3<<8)|(3<<12)|(3<<14)|(3<<19); // HIGH Speed for PA5, PA6, PA7, PA9

SPI1->CR1 |= (SPI_CR1_MSTR | SPI_CR1_SSM | SPI_CR1_SSI);

NVIC_EnableIRQ(TIM2_IRQn); //Prerivania

return 0;

}

#ifdef __cplusplus

}

#endif

Спасибо братцы!

Re: Микроконтроллеры STM32 - тонкости работы, отладочные пла

Пн янв 16, 2023 19:03:09

1. Собака не включена случайно?

2. main покажи

3. __low_level_init() пусть 1 возвращает. Поверь, так будет лучше. Подробности в документации в качестве самообразования.

Добавлено after 4 minutes 13 seconds:

Re: Микроконтроллеры STM32 - тонкости работы, отладочные платы

4. Латентность флэш надо до переключения тактирования настраивать.

5. В Cortex-M глобальные прерывания по умолчанию включены. Если раньше не выключали, нет смысла включать ещё раз.

6. Дёргать ногами через ODR отучайтесь раз и навсегда.

Добавлено after 2 minutes 47 seconds:

Re: Микроконтроллеры STM32 - тонкости работы, отладочные платы

7. Включаете прерывания таймера, а настройка и обработчик где?

2. main покажи

3. __low_level_init() пусть 1 возвращает. Поверь, так будет лучше. Подробности в документации в качестве самообразования.

Добавлено after 4 minutes 13 seconds:

Re: Микроконтроллеры STM32 - тонкости работы, отладочные платы

4. Латентность флэш надо до переключения тактирования настраивать.

5. В Cortex-M глобальные прерывания по умолчанию включены. Если раньше не выключали, нет смысла включать ещё раз.

6. Дёргать ногами через ODR отучайтесь раз и навсегда.

Добавлено after 2 minutes 47 seconds:

Re: Микроконтроллеры STM32 - тонкости работы, отладочные платы

7. Включаете прерывания таймера, а настройка и обработчик где?

Re: Микроконтроллеры STM32 - тонкости работы, отладочные пла

Пн янв 16, 2023 19:10:46

Что такое собака?

По таймеру не стал просто копипастить, вот оно

А как правильно дергать?

Майн

Если правильно понял - поставил первой строкой, не изменилось с экраном(

Я кст пока мучал тактирование и делители плл - 4 платы убил)))

По таймеру не стал просто копипастить, вот оно

- Код:

static uint8_t flagon = 1;

void delay(uint32_t _delay){

TIM2->PSC =9600;

TIM2->ARR = _delay*10;//ms

TIM2->CR1 |= TIM_CR1_CEN;

TIM2->DIER |= TIM_DIER_UIE;

flagon = 1;

while(flagon);}

void TIM2_IRQHandler(void)

{

TIM2->SR &= ~TIM_SR_UIF;

TIM2->CR1 &= ~TIM_CR1_CEN;

flagon = 0;

}

А как правильно дергать?

Майн

- Код:

//Draiver displeja, svistok stm32F411CEU6, TFT 126x160 ST7735

/*3.3v PB3(SPI1_SCK)-SCL

PB5(SPI1_MOSI)-SDA

PB4-RES

PB6-DC (Dannye|Komandy)

PB7-CS

PB8-BL (Pitanie???)

PB10-HL na GND

*/

#include <stddef.h>

#include "stm32f411xe.h"

#include "displey.h"

int main()

{

//GPIOB->ODR |= 0x400;//On svetodiod

GPIOB->ODR |= 0x100;//On podsvetka

LCD_Init();

//bufer();

while(1){

delay(1000);//1s

// GPIOB->ODR |= (1<<8);//On svetodiod

// delay(1000);//1s

// GPIOB->ODR &= ~(1<<8);//On svetodiod

} }

void SystemInit(void){}

Если правильно понял - поставил первой строкой, не изменилось с экраном(

Я кст пока мучал тактирование и делители плл - 4 платы убил)))

- Код:

//Kvarc 25MHz, Proc 100MHzbegin

FLASH->ACR = FLASH_ACR_PRFTEN | FLASH_ACR_ICEN | FLASH_ACR_DCEN | FLASH_ACR_LATENCY_3WS;

RCC->CR = _VAL2FLD(RCC_CR_HSITRIM,16) | RCC_CR_HSION | RCC_CR_HSEON;

while(!(RCC->CR & RCC_CR_HSERDY));

RCC->PLLCFGR = RCC_PLLCFGR_PLLSRC_HSE | _VAL2FLD(RCC_PLLCFGR_PLLQ,4) | _VAL2FLD(RCC_PLLCFGR_PLLN,192) | _VAL2FLD(RCC_PLLCFGR_PLLM,25) | RCC_PLLCFGR_PLLP_div2;

RCC->CR = _VAL2FLD(RCC_CR_HSITRIM,16) | RCC_CR_HSION | RCC_CR_HSEON | RCC_CR_PLLON;

while(!(RCC->CR & RCC_CR_PLLRDY));

RCC->CFGR = RCC_CFGR_MCO2_HSE | RCC_CFGR_MCO2PRE_div1 | RCC_CFGR_MCO1PRE_div1 | RCC_CFGR_I2SSRC_PLLI2S | RCC_CFGR_MCO1_HSE

| _VAL2FLD(RCC_CFGR_RTCPRE,8) | RCC_CFGR_PPRE2_DIV1 | RCC_CFGR_PPRE1_DIV2 | RCC_CFGR_HPRE_DIV1 | RCC_CFGR_SW_PLL;