Nucleo-64 STM32F411 PWM CMSIS

Вт ноя 22, 2022 20:07:19

Не могу включить ШИМ на указанном камне. Использую пин PA5, TIM2.

Дайте пожалуйста подсказку!

На этим пине висит светодиод, хочу плавно повключать его)))

Собственно код:

Дайте пожалуйста подсказку!

На этим пине висит светодиод, хочу плавно повключать его)))

Собственно код:

- Код:

#include "stm32f4xx.h"

//GPIOA5 TIM2_CH1

int main(void) {

RCC->APB1ENR |= RCC_APB1ENR_TIM2EN; // Timer 2 enable

RCC->AHB1ENR |= RCC_AHB1ENR_GPIOAEN; // Port A enable

GPIOA->OSPEEDR |= GPIO_OSPEEDR_OSPEED5_1 | GPIO_OSPEEDR_OSPEED5_0; // High speed

GPIOA->OTYPER &= GPIO_OTYPER_OT5; // PP output

GPIOA->MODER |= GPIO_MODER_MODER5_1; //AF mode

GPIOA->AFR[0] |= GPIO_AFRL_AFRL5_1; //AF1 - timer 2

TIM2->PSC = 800;

TIM2->ARR = 7000;

TIM2->CCR1 = 1000;

TIM2->CCER |= TIM_CCER_CC1E; // Enable timer to output

TIM2->CCER &= TIM_CCER_CC1P; // Select active high polarity

TIM2->CCMR1 |= TIM_CCMR1_OC1M_2 | TIM_CCMR1_OC1M_1; //PWM mode 1

TIM2->CR1 |= TIM_CR1_CEN; // Start timer

while(1){ };

}

Re: Nucleo-64 STM32F411 PWM CMSIS

Вт ноя 22, 2022 22:27:31

- Код:

TIM2->CCER &= TIM_CCER_CC1P; // Select active high polarity

Re: Nucleo-64 STM32F411 PWM CMSIS

Ср ноя 23, 2022 06:08:45

- Код:

TIM2->CCER &= TIM_CCER_CC1P; // Select active high polarity

Убрал эту строчку, результат такой же ;(

Re: Nucleo-64 STM32F411 PWM CMSIS

Ср ноя 23, 2022 08:26:21

- Код:

PA5<PinMode::AF_PushPull_LowSpeed<1>>::mode();

TIM2->PSC = 800;

TIM2->ARR = 7000;

TIM2->CCR1 = 1000;

TIM2->CCMR1 = _VAL2FLD(TIM_CCMR1_CC1S,0) | _VAL2FLD(TIM_CCMR1_OC1M,6) | TIM_CCMR1_OC1PE;

TIM2->CCER = TIM_CCER_CC1E;

TIM2->CR1 = TIM_CR1_CEN;

YuriSh, альтернативная функция пина неправильно задана. GPIO_MODER_MODER5_1 это же двойка.

Пользуйтесь макросами из CMSIS. Вот так меньше вероятность ошибиться _VAL2FLD(GPIO_AFRL_AFSEL5,1);

Оператором &= неправильно пользуетесь. Чтобы сбросить бит в регистре надо вот так делать

- Код:

GPIOA->OTYPER &= ~GPIO_OTYPER_OT5;

Re: Nucleo-64 STM32F411 PWM CMSIS

Ср ноя 23, 2022 09:58:36

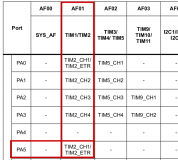

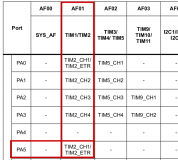

VladislavS, я же правильно понимаю, чтобы настроить пин на режим альтернативной функции мне необходимо первый бит перевести в единицу? разве оно не так делается?

требуется альтернативная функция 1

,

,

следовательно, нулевой бит в единицу:

настроить пин на пуш-пул, сделал, как вы сказали:

Подскажите, пожалуйста, я правильно понял, как выставлять биты в регистрах?

Добавлено after 16 minutes 20 seconds:

В общем разобрался, всем огромное спасибо. Итоговый код:

Ошибка была в строчке

GPIOA->AFR[0] |= GPIO_AFRL_AFRL5_1; //AF1 - timer 2, необходимо было выставить 5_0

- Код:

GPIOA->MODER |= GPIO_MODER_MODER5_1;

требуется альтернативная функция 1

,

,следовательно, нулевой бит в единицу:

- Код:

GPIOA->AFR[0] |= GPIO_AFRL_AFRL5_0

настроить пин на пуш-пул, сделал, как вы сказали:

- Код:

GPIOA->OTYPER &= ~GPIO_OTYPER_OT5;

Подскажите, пожалуйста, я правильно понял, как выставлять биты в регистрах?

Добавлено after 16 minutes 20 seconds:

В общем разобрался, всем огромное спасибо. Итоговый код:

Спойлер

- Код:

#include "stm32f4xx.h"

//GPIOA5 TIM2_CH1

int main(void) {

RCC->APB1ENR |= RCC_APB1ENR_TIM2EN; // Timer 2 enable

RCC->AHB1ENR |= RCC_AHB1ENR_GPIOAEN; // Port A enable

GPIOA->OSPEEDR |= GPIO_OSPEEDR_OSPEED5_1 | GPIO_OSPEEDR_OSPEED5_0; // High speed

GPIOA->OTYPER &= ~GPIO_OTYPER_OT5; // PP output

GPIOA->MODER |= GPIO_MODER_MODER5_1; //AF mode

GPIOA->AFR[0] |= GPIO_AFRL_AFRL5_0; //AF1 - timer 2

TIM2->PSC = 50;

TIM2->ARR = 1000;

TIM2->CCR1 = 200;

TIM2->CCER |= TIM_CCER_CC1P; // Select active high polarity

TIM2->CCMR1 |= TIM_CCMR1_OC1M_2 | TIM_CCMR1_OC1M_1; //PWM mode 1

TIM2->CCER |= TIM_CCER_CC1E; // Enable timer to output

TIM2->CR1 |= TIM_CR1_CEN; // Start timer

while(1){ };

}

Ошибка была в строчке

GPIOA->AFR[0] |= GPIO_AFRL_AFRL5_1; //AF1 - timer 2, необходимо было выставить 5_0

Re: Nucleo-64 STM32F411 PWM CMSIS

Ср ноя 23, 2022 10:27:24

YuriSh, рекомендую поставить бит TIM_CCMR1_OC1PE. Вы же будете рулить скважностью на ходу. И вы злоупотребляете оператором |=. Посмотрите мой код инициализации таймера.

Re: Nucleo-64 STM32F411 PWM CMSIS

Ср ноя 23, 2022 10:35:01

VladislavS, принял, спасибо вам.

Начну глубже изучать битовые операции в С

Начну глубже изучать битовые операции в С

Re: Nucleo-64 STM32F411 PWM CMSIS

Ср ноя 23, 2022 11:32:39

YuriSh, лучше как-то так писать, чтобы понятней было:

Где 5 - номер пина, 1 - значение AF. Сбросить все 4 бита до присваивания нового значения нужно обязательно, если нет уверенности, что эта строчка будет вызываться сразу после инициализации МК (а не где-нибудь, когда в других функциях уже что-то будет туда позаписано или, тем паче, если меняется на лету альтернативная функция).

Можно какой-нибудь макрос забахать, вроде:

и пользоваться как-то так:

У VladislavS все наворочено на шаблонах и констэкспрах С++, а нам, убогим сишникам, приходится макросами выкручиваться…

- Код:

GPIOA->AFR[0] = ((GPIOA->AFR[0] &~GPIO_AFRL_AFRL0)) | 1 << (5 * 4);

Где 5 - номер пина, 1 - значение AF. Сбросить все 4 бита до присваивания нового значения нужно обязательно, если нет уверенности, что эта строчка будет вызываться сразу после инициализации МК (а не где-нибудь, когда в других функциях уже что-то будет туда позаписано или, тем паче, если меняется на лету альтернативная функция).

Можно какой-нибудь макрос забахать, вроде:

- Код:

#define AFRL(n, v) (v << (n*4))

#define AFRH(n, v) (v << ((n-8)*4))

и пользоваться как-то так:

- Код:

GPIOA->AFR[0] = ((GPIOA->AFR[0] &~GPIO_AFRL_AFRL0)) | AFRL(5, 1);

У VladislavS все наворочено на шаблонах и констэкспрах С++, а нам, убогим сишникам, приходится макросами выкручиваться…

Re: Nucleo-64 STM32F411 PWM CMSIS

Ср ноя 23, 2022 12:08:15

Eddy_Em, Интересный способ на макросах, спасибо!

Re: Nucleo-64 STM32F411 PWM CMSIS

Ср ноя 23, 2022 13:26:26

Здесь все корректно ? у сдвига же приоритет выше чем у ИЛИ

GPIOA->AFR[0] = ((GPIOA->AFR[0] &~GPIO_AFRL_AFRL0)) | 1 << (5 * 4);

GPIOA->AFR[0] = ((GPIOA->AFR[0] &~GPIO_AFRL_AFRL0)) | 1 << (5 * 4);

Re: Nucleo-64 STM32F411 PWM CMSIS

Ср ноя 23, 2022 13:46:24

a797945, все корректно. Приоритет же выше!