Помогите с кодом . Хочу разобраться, но не понимаю проблему

Вс дек 25, 2022 20:03:17

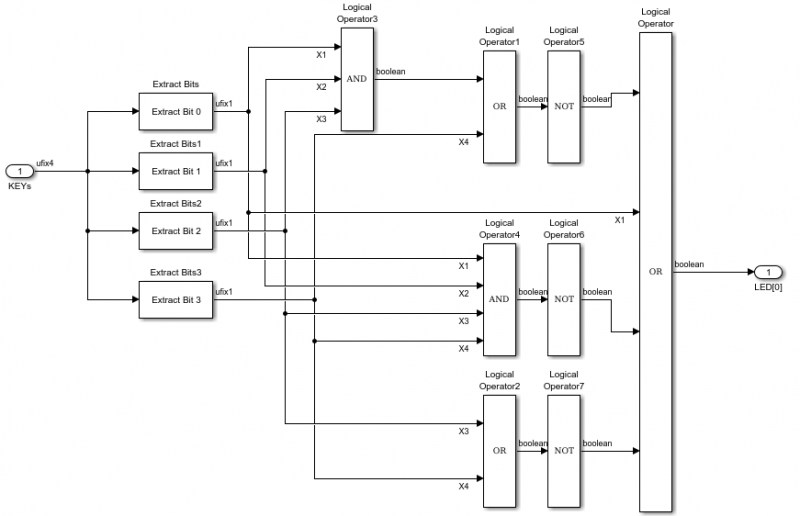

Нужно реализовать с помощью Verilog HDL уравнение

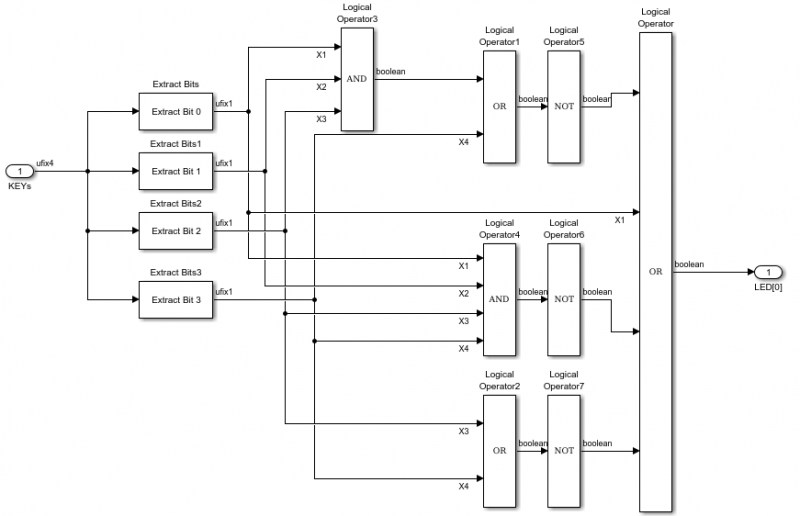

Вторая картинка код, вылезают ошибки, как исправить?

Заранее спасибо за помощь

Вторая картинка код, вылезают ошибки, как исправить?

Заранее спасибо за помощь

- Вложения

-

- Снимок экрана (294).png

- (114.56 KiB) Скачиваний: 91

-

- фффффф.png

- (28.03 KiB) Скачиваний: 68

Re: Помогите с кодом . Хочу разобраться, но не понимаю пробл

Пн дек 26, 2022 18:16:00

Почему у вас вход KEYs, а присванивание идёт по KEY?

Какой сигнал идёт на вывод rst_n?

Что такое и откуда взялось LED[0]?

В общем, смотрите что нагенерил Матлаб для такой схемы:

Какой сигнал идёт на вывод rst_n?

Что такое и откуда взялось LED[0]?

В общем, смотрите что нагенерил Матлаб для такой схемы:

Спойлер

- Код:

// ----------

//

// Generated by MATLAB 9.1 and HDL Coder 3.9

//

//

// -- ----------

// -- Rate and Clocking Details

// -- ----------

// Model base rate: 0

// Target subsystem base rate: 1.#INF

//

// ----------

// ----------

//

// Module: lab3

// Source Path: lab3/lab3

// Hierarchy Level: 0

//

// ----------

`timescale 1 ns / 1 ns

module lab3

(

KEYs,

LED_0

);

input [3:0] KEYs; // ufix4

output LED_0;

wire dtc1; // ufix1

wire X1; // ufix1

wire dtc1_1; // ufix1_E1

wire X2; // ufix1

wire dtc1_2; // ufix1_E2

wire X3; // ufix1

wire Logical_Operator3_out1;

wire X4; // ufix1

wire Logical_Operator1_out1;

wire Logical_Operator5_out1;

wire Logical_Operator4_out1;

wire Logical_Operator6_out1;

wire Logical_Operator2_out1;

wire Logical_Operator7_out1;

wire Logical_Operator_out1;

assign dtc1 = KEYs[0];

assign X1 = dtc1;

assign dtc1_1 = KEYs[1];

assign X2 = dtc1_1;

assign dtc1_2 = KEYs[2];

assign X3 = dtc1_2;

assign Logical_Operator3_out1 = X3 & (X1 & X2);

assign X4 = KEYs[3];

assign Logical_Operator1_out1 = Logical_Operator3_out1 | X4;

assign Logical_Operator5_out1 = ~ Logical_Operator1_out1;

assign Logical_Operator4_out1 = X4 & (X3 & (X1 & X2));

assign Logical_Operator6_out1 = ~ Logical_Operator4_out1;

assign Logical_Operator2_out1 = X3 | X4;

assign Logical_Operator7_out1 = ~ Logical_Operator2_out1;

assign Logical_Operator_out1 = Logical_Operator7_out1 | (Logical_Operator6_out1 | (Logical_Operator5_out1 | X1));

assign LED_0 = Logical_Operator_out1;

endmodule // lab3

Последний раз редактировалось Gudd-Head Пн дек 26, 2022 18:37:27, всего редактировалось 1 раз.

Re: Помогите с кодом . Хочу разобраться, но не понимаю пробл

Пн дек 26, 2022 18:19:14

и разве Quartus не расшифровывает ошибки?

Re: Помогите с кодом . Хочу разобраться, но не понимаю пробл

Вс янв 22, 2023 18:58:25

В логических операциях вместо ! (восклицательный знак) следует использовать ~ (тильда).